System Verilog (SV) Language + Project Demo

- Description

- Curriculum

- Reviews

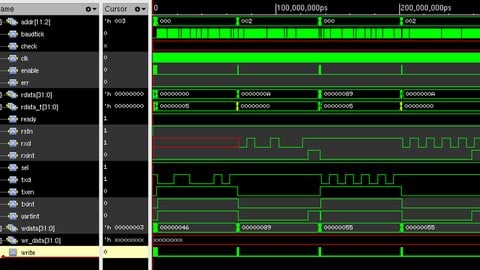

System Verilog course content is designed for beginners to experts ; The modules can be learnt and practiced in couple of weeks: The detailed course syllabus is as follows: It is split into 2 partsSection I:Session 01 • ASIC flow-Design verification and Verilog Refresh Lab 1 – Verilog Testbench developmentSession 02 •System Verilog Introduction, Data Types Lab 2 – Programs with Various data typesSession 03 •Operators-Control Statements-loopsLab 3- SV Constructs practiceSession 04 •Arrays, QueuesLab 4 – Arrays, Queues Constructs practiceSession 05 •OOPs-Classes-Objects Section II:Session 06 •Randomization and ConstraintsLab 6- RandomizationSession 07 •Inter process CommunicationLab 7- Use of mail box, Semaphores and QueuesSession 08 •Interfaces Lab 8-Use of interfaces, mod port, clocking blockSession 09 • Testbench developmentLab 09- Use of SV constructs for driver/BFMSession 10 •Code and Functional Coverage Lab 10-Simulate an example for coverageVarious example codes are explained in the course. Few of the programs are simulated in the industry standard simulators.A protocol example is also taken and testbench code is developed and test cases are written for the project.The assignment given helps to practice the code writing and further using for test bench and testcase development

External Links May Contain Affiliate Links read more