Designing Digital Systems Using VHDL - An introduction

- Description

- Curriculum

- FAQ

- Reviews

Description

In RAHDG 432 we’ll Focus on designing different types of digital systems using VHDL language code then we simulate those in the ISE software and at the end we do the implementation. It includes Design and analysis of latches and flip-flops. Number of digital designs have been designed in VHDL language to make you understand them better.

This course describes the different types of design units in VHDL such as entity, architecture, configuration, package and package body. The design and analysis of synchronous state machines. State minimization and introduction to state assignment. Each topic will have many examples which goes over them briefly with different parts. By end of chapter 2 and 4 there will be a quiz for you to test your understanding of that specific chapter.

Core subject of this course is digital design flow. Topics include PLDs, Flip Flops, latches, Digital Design flow, encoder, signals. By end of the course, you should be able to design, simulate, implement, and troubleshoot our VHDL codes using appropriate techniques and test bench.

This course is mostly for academic level Engineering students in different universities around the world.

Since you would be having a lifetime access to this course you would be able to revisit during your career as year passes to refresh your memory.

Instructor

The instructor of this course is Mehrad Nahouri. He has an Associates in Electrical Engineering concentration on digital field and is a lecturer at Rahsoft.

What is the target audience?

- This course is for students working in VHDL field.

- Undergraduate students

- Electrical Engineer

- Computer Engineer

- Graduate students taking VHDL course

- Researchers in VHDL field

Course content

- Introduction

- Basic Concepts of Digital

- Sequential vs combinational

- SR Latch

- Flip Flops

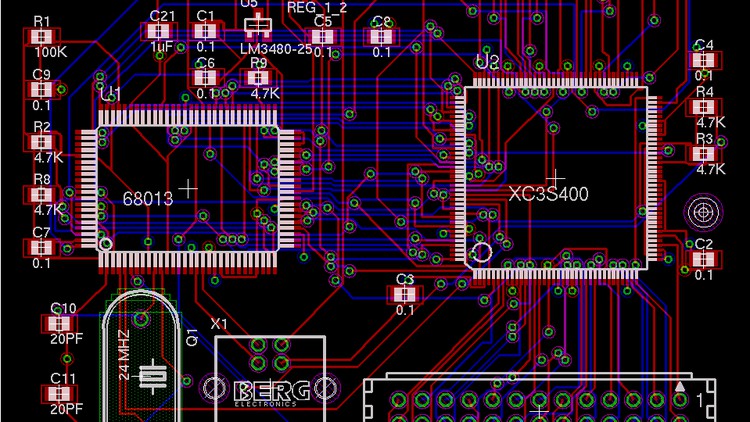

- PLD Family

- FPGA

- VHDL

- FIFO

- ISE Software

- Generic

- Synchronizing

- Test Bench

- ISE Simulation

- BCD code to Excess-3

- Demultiplexer

- Hierarchical and External Naming

Who this course is for:

- Electrical Engineers

- Computer Engineers

- Electrical Engineering Students

- Computer Engineering Students

-

5Basic Concepts of DigitalVideo lesson

-

6Basic Concepts of DigitalVideo lesson

-

7Basic Concepts of DigitalVideo lesson

-

8Sequential vs combinationalVideo lesson

-

9Sequential vs combinationalVideo lesson

-

10Sequential logic ideaVideo lesson

-

11Sequential logic ideaVideo lesson

-

12SR LatchVideo lesson

-

13SR LatchVideo lesson

-

14SR LatchVideo lesson

-

15SR LatchVideo lesson

-

16SR LatchVideo lesson

-

17SR LatchVideo lesson

-

18SR LatchVideo lesson

-

19SR LatchVideo lesson

-

20SR LatchVideo lesson

-

21SR LatchVideo lesson

-

22Timing DiagramVideo lesson

-

23SR Latch Timing DiagramVideo lesson

-

24SR Latch State DiagramVideo lesson

-

25SR LatchVideo lesson

-

26SR Latch with EnableVideo lesson

-

27D LatchVideo lesson

-

28D Latch Timing DiagramVideo lesson

-

29D Latch characteristicVideo lesson

-

30D Latch with transmission gateVideo lesson

-

31D Latch with transmission gateVideo lesson

-

32JK LatchVideo lesson

-

33JK LatchVideo lesson

-

34Flip FlopsVideo lesson

-

35Flip FlopsVideo lesson

-

36D Flip FlopsVideo lesson

-

37D Flip FlopsVideo lesson

-

38D Flip FlopsVideo lesson

-

39D Flip FlopsVideo lesson

-

40Latch vs Flip FlopVideo lesson

-

41Latch vs Flip FlopVideo lesson

-

42Latch vs Flip FlopVideo lesson

-

43Rising Edge D-FFVideo lesson

-

44Rising Edge D-FFVideo lesson

-

45Master Slave FFVideo lesson

-

46T Flip FlopVideo lesson

-

47Asynchronous PresetVideo lesson

-

48Synchronous ResetVideo lesson

-

49Additional Inputs of Flip FlopVideo lesson

-

50Setup time, Hold Time, Delay typesVideo lesson

-

51Setup time, Hold Time, Delay typesVideo lesson

-

52Timing RequirementsVideo lesson

-

53Timing RequirementsVideo lesson

-

54Timing RequirementsVideo lesson

-

55Timing RequirementsVideo lesson

-

56Synchronous vs AsynchronousVideo lesson

-

57Clock SignalsVideo lesson

-

58Synchronous circuitsVideo lesson

-

59Sequential circuit analysisVideo lesson

-

60Sequential circuitVideo lesson

-

61Sequential circuitVideo lesson

-

62Sequential circuitVideo lesson

-

63Sequential circuitVideo lesson

-

64Sequential circuitVideo lesson

-

65State tableVideo lesson

-

66PLD FamilyVideo lesson

-

67Mask Programming DevicesVideo lesson

-

68PLAVideo lesson

-

69GLAVideo lesson

-

70CPLDVideo lesson

-

71CPLD ICVideo lesson

-

72CPLD ArchitectureVideo lesson

-

73FPGAVideo lesson

-

74FPGA ArchitectureVideo lesson

-

75FPGA ArchitectureVideo lesson

-

76FPGA ArchitectureVideo lesson

-

77FPGA & CPLD UsageVideo lesson

-

78FPGA, SystemC, VerilogVideo lesson

-

79ISE InstallVideo lesson

-

80Digital Design FlowVideo lesson

-

81ASIC Digital FlowVideo lesson

-

82System Level Digital FlowVideo lesson

-

83VHDLVideo lesson

-

84Common ComponentsVideo lesson

-

85FIFOVideo lesson

-

86UARTVideo lesson

-

87FIFO operationVideo lesson

-

88General Purpose processorVideo lesson

-

89ISE Software AreaVideo lesson

-

90New Source WizardVideo lesson

-

91ISE Design propertiesVideo lesson

-

92SynthesizeVideo lesson

-

93ISE SchematicVideo lesson

-

94ISE SignalsVideo lesson

-

95ISE warningsVideo lesson

External Links May Contain Affiliate Links read more